15.做的隐式规则

15.1。命令覆盖

问题1:通过各目标的命令拆分写到不同的地方,会发生什么?

<代码>。假的: VAR:=测试 全部: @echo”: $ (VAR) " 包括1.可

文件1.可内容:

<代码>: @echo从1.可“这是命令”

Makefile中出现同名目标时:

依赖:所有的依赖将合并到一起,成为目标的最终依赖

命令:当多处出现同一目标的命令时,让发出警告,所有之前定义的命令被最后的命令取代。

注意:

当使用包括包含其他文件(Makefile)时,需要确保被包含的文件中的同名目标只有依赖,没有命令,否则,同名目标的命令将被覆盖!

15.2。隐式规则

让中提供了一些常用的,例行的规则实现,当目标的规则未提供时,让尝试使用隐式规则

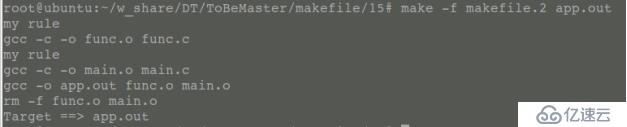

下面的代码可以编译成功吗?为什么?

<代码> src:=$(通配符* . c) obj:=$ (src . c=. o): app.out: $ (obj) $ (CC) - o $ @ $ ^ (RM) ^美元 @echo”目标==比;$ @” %.o: % . c @echo“规则” $ (CC) - c - o $ @ $ ^

根据我们的初步分析,上面的Makefile中存至少两个问题:

1。没有定义CC和RM变量而直接使用

2。没有定义生成. o文件的规则(只有链接没有编译)

运行结果:

makefile(06) _隐式规则

makefile(06) _隐式规则