<强> 1。概述

HDMI英文名为高清晰度多媒体接口,是一种数字化视频,音频接口。现已

广泛应用于高清数字电视,电脑显示器等产品中。

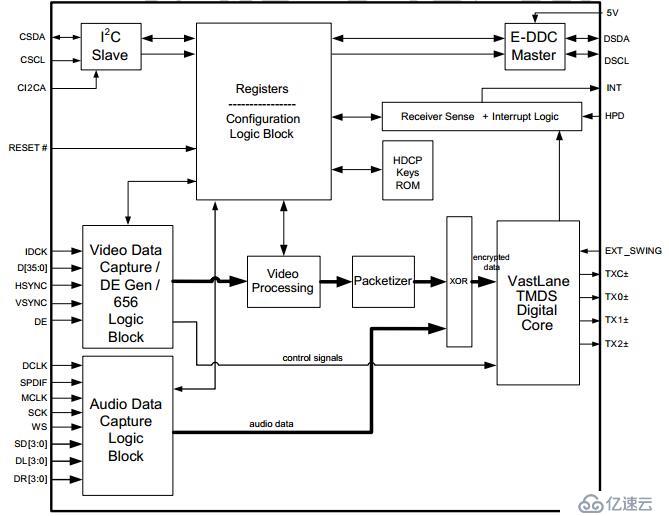

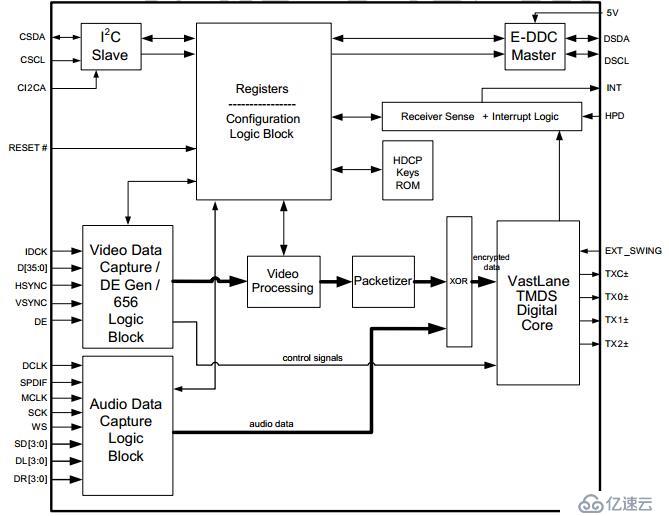

这里我们使用硅形象公司的SiI9134作为HDMI发送芯片,支持HDMI 1.3标准。

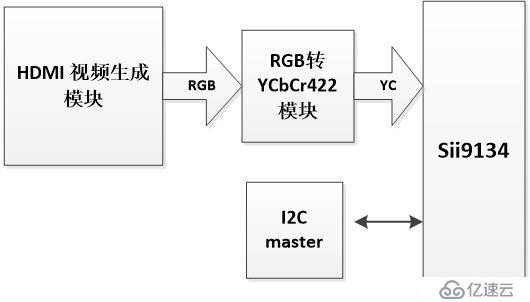

<强> 2。设计框图

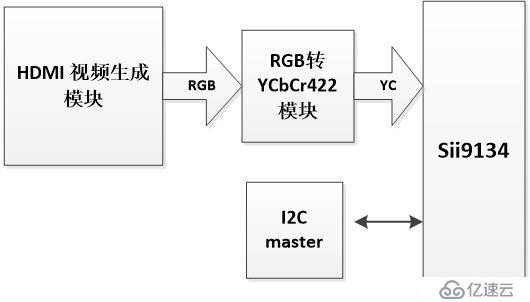

视频源由FPGA内部产生,sii9134的配置通过I2C模块完成。这里以720 p60为例完成设计。

<强> 3。Sii9134配置

这里将Sii9134配置成YCbCr422输入,RGB444输出模式。

void sii9134_init ()

{

,,,sccb_senddata (0 x72 0 x05 0 x01);//reset all 部分

,,,sccb_senddata (0 x72 0 x05 0 x00);//disable 重置

,,,sccb_senddata (0 x72 (0 x37);//VSYNC 以及HSYNC, 24位,rising 边缘,normal 操作

,,,sccb_senddata (0 x72 0 x0c 0 x00);

,,,sccb_senddata (0 x72 0 x0d 0 x01);

,,,sccb_senddata (0 x72 0 x4b 0 x00);//蓝色

,,,sccb_senddata (0 x72 0 x4c 0 x00);//绿色

,,,sccb_senddata (0 x72 0 x4d 0 xff);//红色

,,,sccb_senddata (0 x72 0 x82 0 25);//FPLL * IDCK enable internal source 终止

,,,sccb_senddata (0 x72 0 x83 0 x19);//HDMI 锁相环/2,PLL filter 反?4,PLL filter 前/2

,,,sccb_senddata (0 x72 0 x84 0 x31);//50 ua PLL filter post/2

,,,sccb_senddata (0 x72 0 x85 0 x01);//HDMI transmitter PLL 前/2

,,,sccb_senddata (x32 0 x72 0, 0 x04);//h-blank

,,,sccb_senddata (0 x72 0 x33 0 x41);//enable 德,positive 极性,,留空(370,像素)

,,,sccb_senddata (0 x72 0 x34 0 x19);//v-blank(30,行)

,,,sccb_senddata (0 x72 0 x36 0 x00);//从而width of active 显示

,,,sccb_senddata (0 x72 0 x37 0 x05);//从而width of active 显示器(1280)

,,,sccb_senddata (0 x72 0 x38 0 xd0);//从而height of active 显示

,,,sccb_senddata (0 x72 0 x39 0 x02);//从而height of active 显示器(720)

x3e x72 sccb_senddata (0, 0, 0 x00);

sccb_senddata (0 x72 0 x40 0 x6e);

sccb_senddata (0 x72 0 x41 0 x00);

x44 x72 sccb_senddata (0, 0, 0 x29);

x45 x72 sccb_senddata (0, 0, 0 x00);

x46 x72 sccb_senddata (0, 0, 0 x05);

x72 sccb_senddata(0, 0开发,x47 0 x06);

x48 x72 sccb_senddata (0, 0, 0 x30);

x49 x72 sccb_senddata (0, 0, 0 x00);

x4a x72 sccb_senddata (0, 0, 0 x3c);////////////////////////////////////////////////sccb_senddata (0 x7a 0 x01 0 x02);

sccb_senddata (0 x7a 0 x02 0 x01);

sccb_senddata (0 x7a 0 x03 0 x00);

x04 x7a sccb_senddata (0, 0, 0 x18);

x05 x7a sccb_senddata (0, 0, 0 x00);

x7a sccb_senddata (0, 0 x14, 0 x11);

x1d x7a sccb_senddata (0, 0, 0 x40);

x21 x7a sccb_senddata (0, 0, 0 x02);

x7a sccb_senddata(0, 0将0 x2b);

x2f x7a sccb_senddata (0, 0, 0 x01);

sccb_senddata (0 x7a 0 x40 0 x82);

sccb_senddata (0 x7a 0 x41 0 x02);

×x7a sccb_senddata (0, 0, 0 x0d);

x43 x7a sccb_senddata (0, 0, 0 x59);

x44 x7a sccb_senddata (0, 0, 0 x11);

x45 x7a sccb_senddata (0, 0, 0 x28);

x46 x7a sccb_senddata (0, 0, 0 x00);

x7a sccb_senddata(0, 0开发,x47 0 x04);

x48 x7a sccb_senddata (0, 0, 0 x00);

x49 x7a sccb_senddata (0, 0, 0 x00);

x4a x7a sccb_senddata (0, 0, 0 x00);

x4b x7a sccb_senddata (0, 0, 0 xd1);

x4c x7a sccb_senddata (0, 0, 0 x02);

x4d x7a sccb_senddata (0, 0, 0 x00);

x4e x7a sccb_senddata (0, 0, 0 x00);

x4f x7a sccb_senddata (0, 0, 0 x01);

×50 x7a sccb_senddata (0, 0, 0 x05);

x7a sccb_senddata (0, 0 x51 0 x00);

x52 x7a sccb_senddata (0, 0, 0 x00);

sccb_senddata (0 x7a 0 x80 0 x84);

x81 x7a sccb_senddata (0, 0, 0 x01);

x82 x7a sccb_senddata (0, 0, 0 x0a);

x7a sccb_senddata (0, 0 x83 0 x70);

x84 x7a sccb_senddata (0, 0, 0 x01);

sccb_senddata (0 x7a 0 x85 0 x00);

x86 x7a sccb_senddata (0, 0, 0 x00);

x87 x7a sccb_senddata (0, 0, 0 x00);

x88 x7a sccb_senddata (0, 0, 0 x00);

x89 x7a sccb_senddata (0, 0, 0 x00);

x8a x7a sccb_senddata (0, 0, 0 x00);

x8b x7a sccb_senddata (0, 0, 0 x00);

x8c x7a sccb_senddata (0, 0, 0 x00);

x8d x7a sccb_senddata (0, 0, 0 x00);

x3e x7a sccb_senddata (0, 0, 0 x33);

}

<强> 4。FPGA逻辑设计

FPGA逻辑完成视频源生成,HDMI配置,RGB转YCbCr功能。下面表格给出RGB转YC的公式。