<强> 1。概述,

本设计采用FPGA技术,将CMOS摄像头(LVDS接口)的视频数据经过采集,存储,帧率转换及格式转换,最终通过USB2.0接口显示在电脑屏幕上。

<强> 2。硬件系统框图

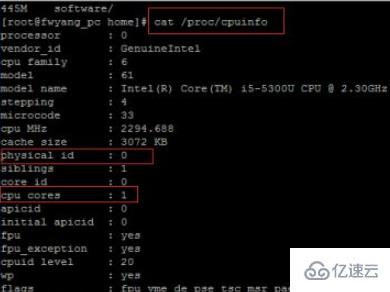

CMOS采用一款全局曝光芯片,FPGA采用阿尔特拉公司的气旋,FLASH采用EPCS64, DDR2采用海力士公司的1 gb内存条,USB2.0采用柏树公司的68013芯片。

<强> 3。FPGA逻辑框图

FPGA各部分逻辑模块如下图所示:

LVDS解码,解码CMOS摄像头视频数据;

I2C的主人,配置CMOS芯片;

DDR2控制,配置与控制DDR2芯片组,实现读写仲裁;

FIFO写,将采集到的视频数据跨时钟域地写进DDR2中;

FIFO阅读,将DDR2中的数据跨时钟域地读出给后续图像处理模块;

帧缓冲,负责FIFO写和FIFO读的调度,实现帧率转换;

USB控制,接受USB PHY的请求,通过FIFO的看向DDR2索取数据,并自定义打包发送给USB PHY芯片。

<强> 4。全局曝光

全局曝光是针对逐行曝光的改进,在逐行曝光下,传感器是按照行为单位进行逐行曝光,这样当被摄物体和传感器存在高速的相对运动时,图像会发生形状和颜色的变形,如下图所示:

<强> 6。CMOS配置

CMOS传感器支持最高130年万像素,240帧的视频输出。

SpiWriteRegister (0 x01 0 x03 0 x01);//soft 重置

SpiWriteRegister (0 x01 0 x00 0 x00); SpiWriteRegister (0 x30 0 x34 0 x01); SpiWriteRegister (0 x30 0 x35 0 xc2);

x0b x33 SpiWriteRegister (0, 0, 0 x4c); SpiWriteRegister (0 x36 0 x64 0 x09); SpiWriteRegister (0 x36 0 x38 0 x82);

x3d SpiWriteRegister (0, 0 (0 x00); SpiWriteRegister (0 x36 0 x40 0 x03); SpiWriteRegister (0 x36 0 x28 0 x07);

x05 x32 SpiWriteRegister (0, 0, 0 x93);//共和党全国委员会

SpiWriteRegister (0 x36 0 x20 0×); SpiWriteRegister (0 x36 0 x23 0 x06); SpiWriteRegister (0 x36 0 x27 0 x02);

x21 x36 SpiWriteRegister (0, 0, 0 x28); SpiWriteRegister (0 x36 0 x3b 0 x00); SpiWriteRegister (0 x36 0 x33 0 x24);

x34 x36 SpiWriteRegister (0, 0, 0 xff);,,//fpn 优化

x34 SpiWriteRegister (0, 0 x16, 0 x10); SpiWriteRegister (0 x3e 0 x03 0 x0b); SpiWriteRegister (0 x3e (0 x03);

x09 x3e SpiWriteRegister (0, 0, 0 x20); SpiWriteRegister (0 x3e 0 x01 0 x23);

x3e SpiWriteRegister (0, 0 x14, 0 xb0); SpiWriteRegister (0 x33 0 x0b 0 x40); SpiWriteRegister (0 x3e (0 x3f);

x3b x36 SpiWriteRegister (0, 0, 0 x80); SpiWriteRegister (0 x36 0 x23 0 x07); SpiWriteRegister (0×50 0 x00 0 x01);

SpiWriteRegister (0 x3e 0 x01 0 x00); SpiWriteRegister (0 x3e 0 x02 0 x30); SpiWriteRegister (0 x32 0 x0c 0 x05);

x32 SpiWriteRegister (0, 0 x0d 0 x46); SpiWriteRegister (0 x32 0 x0e 0 x02);

SpiWriteRegister (0 x32 0 x0f 0 x58); SpiWriteRegister (0 x36 0 x38 0 x85); SpiWriteRegister (0 x33 0 x06 0×50);

x0b x33 SpiWriteRegister (0, 0, 0 x68); SpiWriteRegister (0 0 x33 (x10); SpiWriteRegister (0 x3e 0 x01 0 x00);

x3b x36 SpiWriteRegister (0, 0, 0 x00); SpiWriteRegister (0 x36 0 x63 0 xf8); SpiWriteRegister (0 x36 0 x64 0 x0a);

x33 x36 SpiWriteRegister (0, 0, 0 x27); SpiWriteRegister (0 x30 0 x3a 0 x3a);

SpiWriteRegister (0 x30 0 x3a 0 x3a); SpiWriteRegister (0 x30 0 x3a 0 x3a); SpiWriteRegister (0 x30 0 x3a 0 x3a);

x3b x36 SpiWriteRegister (0, 0, 0 x00); SpiWriteRegister (0 x34 0 x16, 0 x38); SpiWriteRegister (0 x3e (0 x23);

SpiWriteRegister (0 x3c 0 x00 0 x41);,//FIFO RESET for mipi

SpiWriteRegister (0 x30 0 x19 0 x00);

SpiWriteRegister (0 x30, 0 x31 0 x0a);//, 10位

SpiWriteRegister (0 x30 0 x00 0 x00); SpiWriteRegister (0 x30 0 x01 0 x00); SpiWriteRegister (0 x30 0 x39 0 x20);

SpiWriteRegister (0 x30 0 x3a 0 x31); SpiWriteRegister (0 x30 0 x3b 0 x02); SpiWriteRegister (0 x30 0 x3c, ();

SpiWriteRegister (0 x4b 0 x00 0 xa2);,//must

SpiWriteRegister (0 x30 0将0 x19);//必须

SpiWriteRegister (0 x30 0 x3f 0 x01);//必须

SpiWriteRegister (0 x30 0 x30 0 x04);//必须

SpiWriteRegister (0 x30 0 x2b 0 xa0);//必须

SpiWriteRegister (0 x36 0 x20 0 x43); SpiWriteRegister (0 x36 0 x21 0 x18); SpiWriteRegister (0 x45 0 x01 0 xc0);

SpiWriteRegister (0 x45 0 x02 0),,//br recieve inv

x23 x36 SpiWriteRegister (0, 0, 0 x07); SpiWriteRegister (0×50 0 x00 0 x01); SpiWriteRegister (0 x36 0 x20 0 x43);

SpiWriteRegister (0 x33 0 x00 0 x30); SpiWriteRegister (0 x3e 0 x01 0 x14); SpiWriteRegister (0 x36 0 x3b 0 x80);

x64 x36 SpiWriteRegister (0, 0, 0 x0a); SpiWriteRegister (0 x3e (0 x23);

x34 SpiWriteRegister (0, 0 x16, 0 x00); SpiWriteRegister (0 x36 0 x33 0 x20);

x33 x36 SpiWriteRegister (0, 0, 0 x23); SpiWriteRegister (0 x32 0 x11, 0 x0c); SpiWriteRegister (0 x3e 0 x0f 0 x05);

x3b x36 SpiWriteRegister(0, 0, 0();//红外系统

x33 x36 SpiWriteRegister(0, 0, 0将);//nvdd

SpiWriteRegister (0 x33 0 x02 0 x0c);//rst go 低

x33 SpiWriteRegister (0, 0 x83 0 x0a);//, pbias en rise 边缘

x23 x36 SpiWriteRegister (0, 0, 0 x04);

x82 x33 SpiWriteRegister (0, 0, 0 x0f);//sa fall 边缘

SpiWriteRegister (0 x3e 0 x0f 0 x84);,,//收益

x0e x3e SpiWriteRegister (0, 0, 0 x03);,,//收益

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null

null